지난 시간엔 CMOS 로직 게이트 딜레이, 즉 propagation delay에 대해서 공부했어요.

그리고 단위 사이즈 인버터의 딜레이를 계산하는 예제까지 접해보았죠.

오늘은 팬아웃, 그리고 큰 로드를 구동하기 위해서 게이트 스테이지를 나누면 좋은 이유를 공부할 거예요.

fan-out 이란?

Fan-Out 이란? Fan Out 정의

fan out 은 로직 게이트에서 하나의 출력이 (최대) 몇 개의 입력을 구동할 수 있는지를 말한다.

이때 회로의 동작을 저해하지 않는 한에서 갯수를 의미한다.

Fan-Out 4 인버터 예제

지난 시간에 공부했던 size 1의 single inverter를 고려해보자.

unit size inverter란 Width Wp 가 Kp만큼 사이징 되어 Kp x Wn 이었고 ( 따라서 pmos와 nmos의 driving strength가 동일)

Wn은 Wmin ( = 8 Lmin ) 이었다.

한 개의 unit size inverter 가 동일한 사이즈의 inverter 4개를 구동한다고 하자.

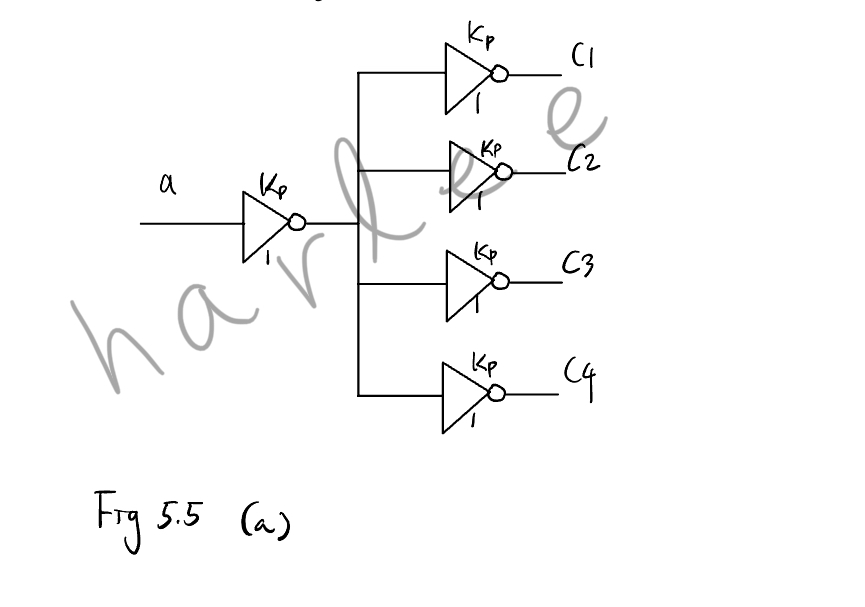

그림 5.5(a)처럼 그릴 수 있고, Fan-Out은 4이다.

RC 딜레이 모델로 나타내면 아래 그림 5.5 (C) 처럼 그려서 나타낼 수 있다.

(c) 는 RC delay 계산 측면에서 (a)와 equivalent circuit이다.

Fan Out 4에서는 inverter 1 개를 구동할 때 대비 ...

- Driving Resistance인 Rn은 그대로이다.

- 로드의 Input Cap은 4배증가 했다. ( 맞지? 4개 인버터 게이트 인풋노드를 를 충 방전 시켜야함 ... )

따라서 일반적으로 fan-Out F에 대한 delay는 다음처럼 표현할 수 있다.

t_F = F * t_inv

( unit inverter delay의 F 배가 됐다. )

28n 공정에서 t_inv 가 대략 2.7ps 였으므로

fan out 4, 즉 F= 4 일 때 t_4 = 10.8ps 로 계산 가능하다.

사실 이건 unit size inv 4개가 아니라 4배 사이즈의 inverter를 구동할 때와도 동일하다.

아래 그림 (b)

참 쉽죠잉?

그러나 .. ! ..! ..! 오늘의 중요 lesson

매우 큰 fan-out은 하나의 게이트로 한 번에 구동하기보다는 stage를 나누어 구동하는 것이 좋다.

그렇게 하면 delay가 Fan-Out에 대해 linear가 아닌 logarithmetically 증가한다.

1024배 Large Load 구동 예제

위 그림처럼 unit size inverter 한 개가 fan-out 1024의 아주 큰 로드를 구동해야하는 상황을 가정해본다.

그냥 구동하면 delay는 1024배가 되지만,

bN 과 xN 사이 로직 게이트 스테이지를 나눔으로써 최소의 딜레이를 얻을 수 있다. (한번 해보자능)

최소 딜레이를 얻기 위해서 각 stage 별로 구동력이 동일한 배수(factor)로 증가하는 inverter들의 체인으로 stage를 나누어 본다.

이 예제의 경우는 각 stage마다 inv 구동력이 4배가 된다.

stage를 나누기 전에는 bN을 xN에 그대로 연결했더라면 delay는 1024 t_inv가 되었을 것이다.

그러나 그림처럼 5 stage로 나누면 4 t_inv + 4 t_inv + 4 t_inv + 4 t_inv + 4 t_inv = 20 t_inv 로..

딜레이를 확 줄일 수 있다.

딜레이가 fan-out에 linear하게 증가( 1024 t_inv)한 것이 아니라 logarithmatically 증가 ( 4 * log_4 1024 = 4 * 5 = 20 t_inv) 했다.

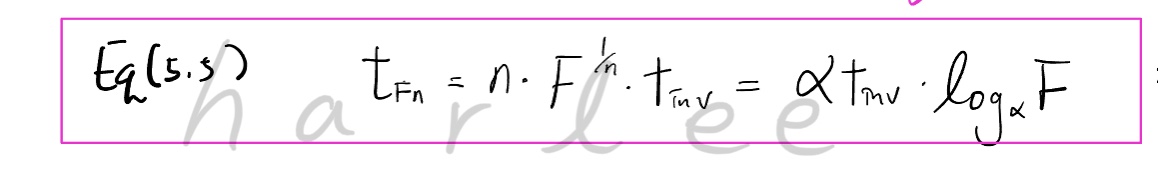

이러한 stage 갯수( n ) 와 fan-out(F), delay(t_Fn)의 관계를 일반화하여 공식으로도 표현 가능하다.

( α 은 각 stage별 fan-out)

위 공식을 n에 대해서 미분하면

α = e 일때 t_Fn이 최소가 된다.

실질적으로는 각 stage 마다 fan-out이 3~6일 때, 결과가 가장 좋다.

관습적으로 fan-out of 4를많이 사용한다.

fan-out of α 로 각 stage를 나누게 되면

total F 에 비례하는 딜레이가 아닌 log_α F 로 줄어든 딜레이를 얻을 수 있다.

'Digital Design' 카테고리의 다른 글

| 1. 디지털 시스템 디자인 서론 (3) | 2024.07.10 |

|---|---|

| Digital Circuit의 Static Path Delay 계산하기 (3) Fan-In, Logical Effort의 정의 (3) | 2024.06.22 |

| CMOS gate의 static delay (1) - Propagation delay (2) | 2024.06.07 |