지난 시간 Fan-out이 path delay에 미친 영향에 대해서 공부했다.

이번 시간에는 Fain-In이 Path Delay에 미치는 영향에 대해서 공부한다.

Fan-Out은 로직게이트의 출력이 다음 단에서 최대 몇개의 게이트 입력을 구동할 수 있는가였습니다.

Fan-In은 로직게이트의 입력단에 최대로 연결될 수 있는 갯수입니다. 즉, 게이트 입력의 갯수(?)

Fan-In은 드라이빙게이트의 output resistance를 증가시킴으로써 딜레이에 영향을 줍니다..

우리의 모든 딜레이 계산은 unit-size inverter를 기준으로 합니다.

따라서 fan-in의 영향을 받은 게이트가 unit-size inverter 대비 얼만큼 딜레이가 증가했는지를 모델링하기 위해,

우선 게이트의 output drive를 constant로 고정시켜놓고 계산합니다.

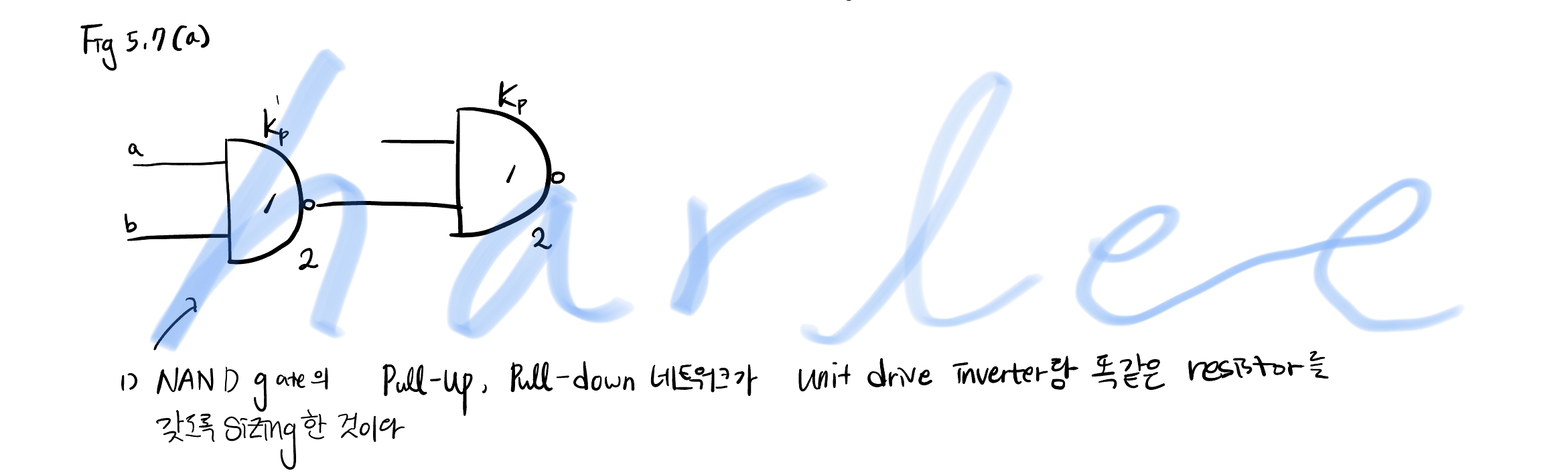

다시 말해 multi-input gate들의 tr들을 적절하게 sizing 하여

pull-down network와 pull-up network의 resistance가 unit-size inverter예제와 같아지도록 만듭니다.

예를들어 2-input NAND 게이트가 자신과 똑같은 놈을 구동시킨다고 할 때…

pull-up network를 구성하는 pmos들의 width는 Kp가 되어야 하고

pull-down network를 구성하는 nmos들의 width는 2가 되어야 한다.

왜냐하면 2-input NAND Gate의 tr level schematic은 아래와 같은데

pull-up network의 worst case resistance는 입력이 한 개만 켜졌을 때이다. ( 보통 딜레이 계산할 때 우리는 worst case delay를 고려한다. )

따라서 pmos 각각을 inv와 같은 Kp로 sizing 해준다.

pull-down network는 2개 인풋이 다 켜져야만 전류가 흐른다.

따라서 저항의 직렬 연결이므로 width를 2배 키운다.

저항이 2배 커졌으므로 동일한 전류를 유지시키기 위해 2배 크게 잡아야 한다.

다시 정리해보자.

unit size inv에 비해서 Fan-in이 증가한 2-input NAND Gate의 딜레이를 계산하기 위해서

일단 구동게이트(driving gate)의 driving capability, 즉 output resistance를 동일하게 만들어놓고 시작한다.

이렇게 사이즈를 맞춰놓고, fan-in의 영향에 대해서만 증가한 딜레이를 구하는 것이다.

그러고 게이트의 사이즈가 달라진다면, 사이즈에 대한 요소만 여기서 곱해주면 된다.

즉 딜레이에 영향을 주는 두 가지 요소를 쪼개서 생각해서 각각을 곱해주는 과정을 거치는 것이다.

드라이빙 게이트가 인버터랑 동일한 전류로 동작하도록 사이징 되어 있을때, fan-in에 대한 영향을 구해두고

거기다 사이즈에 관한 영향을 곱하기 위한 과정이다.

unit size inverter 끼리만 연결 했을 때

input capacitance 는 ( 1+Kp ) C_G 였다.

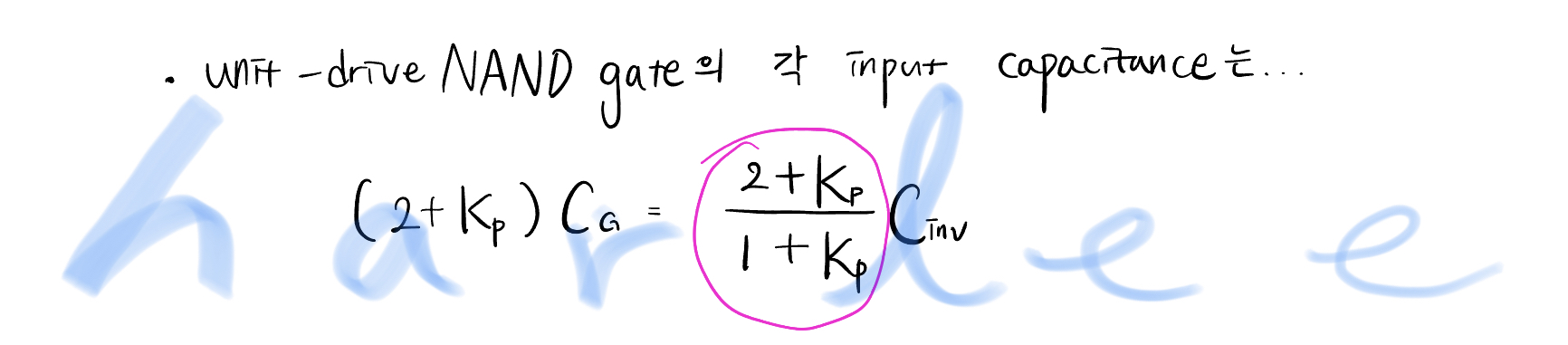

그런데 unit size inv와 동일한 구동력을 가진 2 - input NAND gate끼리 연결 했을 때,

input capacitance는 (2+Kp) C_G 이다.

따라서 다음과 같이 표현할 수 있다.

이렇게 unit-size inverter와 동일한 output drive대비 증가한 input capacitance의 증가율을 Logical Effort라고 한다.

Logical Effort 정의

교재에 나타난 정의

It represents the effort (in additional charge that must be moved compared to an inverter) to perform the two-input NAND logic function.

유닛 사이즈 인버터 대비, 2-INPUT NAND Gate를 동작시키기 위해 추가적으로 대전시켜야 하는 전하량…

(즉 증가한 input cap의 양)

무슨일이 일어났나요?

Fan-In의 영향을 output 쪽에서 나타도록 밀어내버림 ㅎㅎ

따라서 동일한 gate를 구동(drive)하는 데 필요한 delay는 t_inv에 Logical Effort를 곱한 값이다.

Multiple Input NAND 와 NOR 의 Logical Effort 표

위 표는 28nm 공정 기준.. 그러니까 이 교재가 쓰인 시기인 아주 오래전 공정 기준이에요.

NAND Gate의 Logical Effort

Pull-Up Network의 worst case는 pmos가 하나만 켜지는 경우에요.

이때 unit size inv와 rising propagation delay가 동일하려면 ( 즉 Pull-Up Network의 output resistance 가 같으려면 )

width를 Kp로 사이징 해줍니다. (결국 PUN에 pmos한 개 였던 inv랑 똑같음 )

Pull-Down Network는 켜지려면 모든 nmos가 다 켜져야해요. 왜냐하면 F개 nmos들이 전부 직렬로 연결되었기 때문이에요.

저항의 직렬 연결은 덧셈입니다.

따라서 unit size inv 대비 저항이 F 배 증가했어요.

그렇기 때문에 NMOS는 각각을 F배 큰 width로 사이징해주어야 unit size inv 대비 동일한 전류를 흘리는, 즉 동일한 output resistance를 갖게 돼요.

따라서…

이렇게 Fan-in F의 NAND gate의 Logical Effort를 일반화하면..

이때 증가한 delay는 t_inv에 Logical Effort를 곱한 것으로..

NOR Gate의 Logical Effort

NOR gate는 반대로 pull-up network의 pmos 들이 series로 연결되므로

PMOS의 width는 F*Kp 가 되어야 하고

NMOS width는 unit-size inv와 동일한 1로 만들어준다.

따라서 Fan-in F의 NOR Gate의 Logical Effort를 일반화 하면

마찬가지로 delay는 t_inv 에 Logical Effort를 곱한 값이다.

다른 gate들의 logical effort

NAND나 NOR 말고 다른 Logic Gate들에 대해서도 Logical Effort는 동일한 방식으로 계산한다.

예제 하나 보고 갈래?

3 input AOI gate의 Logical Effort

얘는 좀 까다로운게 NAND나 NOR와 다르게

3개 input에 대한 input capacitance가 다르다.

따라서 Logical Effort도 각각 계산해주어야 한다.

3 input AOI gate의 생김새는..

AOI는 And Or Inverter의 약어이다.

input b, c를 AND하고

그 결과를 input a 와 OR하고

최종 결과를 INVERT한다.

(AND - OR - INV)

위 그림에서 5.8(b)는 tr level circuit으로 그린 것인데..

먼저 해주어야 할 것이 각 tr들의 사이즈를 정해주는 것이다.

어떻게? unit size inv랑 동일한 구동력을 갖도록!

Pull Up Network는 b와 c 둘중 하나만 켜지고 a는 켜지는 상황이 worst case이다.

a는 항상 켜져야 한다. 안그러면 Pull-Up Network가 켜지지 않으니까.

따라서 이때는 두 개의 PMOS가 직렬로 연결된 것과 같은데, 그러면 저항이 2배 증가하니까

PMOS들은 unit size inv 보다 두 배 크게, 2*Kp로 사이징 해준다.

Pull Down Network는 b와 c에 연결된 NMOS들이 켜지는 path가 worst case이다.

따라서 b와 c에 연결된 NMOS는 unit size inv보다 두 배 크게, 2로 사이징해준다.

a와 연결된 NMOS는 unit size inv와 동일한 저항을 가지므로 1로 사이징해준다.

이렇게 모든 tr 들의 사이징이 끝나면, 각 입력 a, b, c 에 대해 증가한 input capacitance의 비율, 즉 Logical Effort를 얻을 수 있다.

그럼 이제 실전!!

Digital Circuit의 Path Delay 구하기

문제 파악

- a, bN, c, dN, e 스테이지는 각각 unit size inv 와 동일한 구동력을 갖돼, input cap이 1, 4, 4, 8, 32배 커지도록 사이징 되어 있다.

- 3 in NOR의 Logical Effort 는 2.43이다.

- 2 in NAND의 Logical Effort 는 1.29이다.

계산

- a ~ bN단에서의 delay : t_inv * 4 * 1 -> inv의 logical effort는 1이다. Fan-Out은 4이다.

- bN ~ c 단에서의 delay : t_inv * 1 * 2.43 -> 3in NOR의 L.E는 2.43이다. Fan-Out은 1 (1/4 R * 4 C) 이다.

- c~ dN 단에서의 delay : t_inv * 2 * 1.29 -> 2in NAND의 L.E는 1.29이다. Fan-Out 은 2 ( 1/4 R * 8C ) 이다.

- dN ~ e단에서의 delay : t_iv * 4 * 1 -> inv의 L.E는 1이다. Fan-Out은 4 (1/8 R * 32 C) 이다.

따라서 Path Delay는 (4 + 2.43 + 2.58 +4 ) t_inv = (약) 13 t_inv 이다.

문제 해결 전략 :

signal의 fan-out과 logical effort를 계산한다.

그리고 그들을 곱하면 해당 stage에서 delay가 계산된다.

t_inv는 stage delay의 합이다.

'Digital Design' 카테고리의 다른 글

| 1. 디지털 시스템 디자인 서론 (3) | 2024.07.10 |

|---|---|

| CMOS gate의 static delay (2) - Fan-Out / Driving Larg Loads (3) | 2024.06.16 |

| CMOS gate의 static delay (1) - Propagation delay (2) | 2024.06.07 |